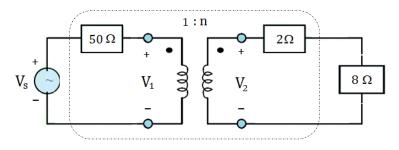

Q.3 (a) As depicted in the figure below, a practical transformer is used to transfer electric power from an AC source Vs with an RMS value of 180V to a  $8\Omega$  loudspeaker.

Practical Transformer

The practical transformer with a turn ratio n = 0.5 is modeled as a resistor in series with an ideal coil in both primary and secondary windings, respectively. Determine the average power consumed by the loudspeaker and the average power consumed by the transformer. What does the transformer do with the power consumed? What is the power efficiency of the whole transformer circuit?

(15 Marks)

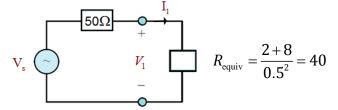

Solution: Using the equivalent impedance of the transformer, we have

Thus,

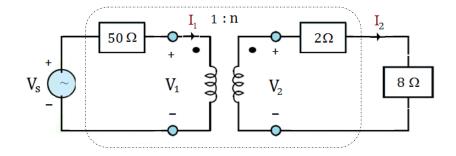

$$I_1 = \frac{V_s}{50 + 40} = \frac{180 \angle 0^\circ}{90} = 2 \angle 0^\circ, \qquad V_1 = I_1 R_{\text{equiv}} = 80 \angle 0^\circ$$

$$V_2 = nV_1 = 40 \angle 0^\circ, \qquad I_2 = \frac{I_1}{n} = \frac{2\angle 0^\circ}{0.5} = 4\angle 0^\circ$$

$P_{\text{loudspeaker}} = |I_2|^2 R_{\text{loudspeaker}} = 4^2 \cdot 8 = 128 \text{ W}$

$P_{\text{transformer}} = |I_1|^2 R_{50\Omega} + |I_2|^2 R_{2\Omega} = 2^2 \cdot 50 + 4^2 \cdot 2 = 232 \text{ W}$ , which heats up the transformer!

The power efficiency =  $\frac{128}{128 + 232} = 35.56\%$

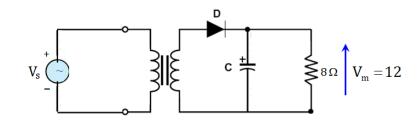

Q.3 (b) A half wave rectifier shown in the figure below is connected to an  $8\Omega$  load resistor. Assume that the transformer, the diode and the capacitor are all ideal, and the output voltage is smooth.

Determine the total power supplied by the source.

(10 Marks)

**Solution:** Since the transformer, the diode and the capacitor are all ideal, they all do not consume any power. Thus, the power consumed by the load resistor is the power supplied by the source. Since the output voltage is smooth, i.e., it is a pure DC voltage, the power consumed by the load resistor is given by

$$P_{\text{source}} = P_{\text{load}} = \frac{V_{\text{m}}^2}{R_{\text{load}}} = \frac{12^2}{8} = 18 \text{ W}$$

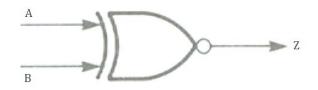

Q.4 (a) Shown in the figure below is an exclusive OR NOT gate, i.e., it is a cascade of an exclusive OR gate together with a NOT gate. Construct its truth table. Can you implement it using other logic gates? If yes, draw any one of its implementations.

(10 Marks)

## **Solution:** The truth table:

| А | В | $A \oplus B$ | $Z = \overline{A \oplus B}$ |

|---|---|--------------|-----------------------------|

| 0 | 0 | 0            | 1                           |

| 0 | 1 | 1            | 0                           |

| 1 | 0 | 1            | 0                           |

| 1 | 1 | 0            | 1                           |

Yes, we can implement this exclusive OR NOT gate using other logic gates. From the above truth table, we have

$$Z = \overline{A \oplus B} = \overline{A} \cdot \overline{B} + A \cdot B$$

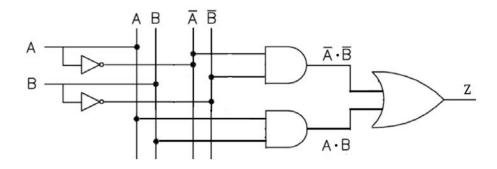

The following is one of its implementation:

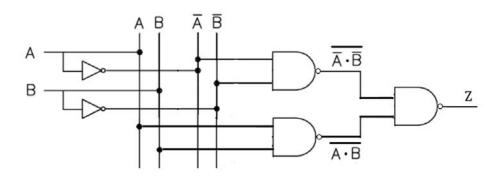

Note that the implementation for Z is non-unique. Here is another one:

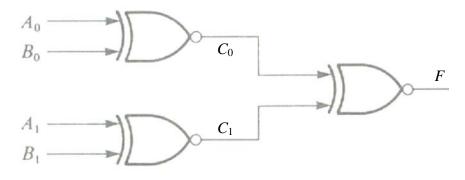

Q.4 (b) The logic circuit shown below is one part of the magnitude comparator used to compare two binary numbers  $(A_1 A_0)$  and  $(B_1 B_0)$ . Construct its truth table.

(10 Marks)

## Solution:

| $A_0$ | $B_0$ | <i>C</i> <sub>0</sub> | $A_1$ | $B_1$ | <i>C</i> <sub>1</sub> | F | $(A_0 \ A_1)$ | $(B_0 \ B_1)$ |

|-------|-------|-----------------------|-------|-------|-----------------------|---|---------------|---------------|

| 0     | 0     | 1                     | 0     | 0     | 1                     | 1 | (00)          | (00)          |

| 0     | 0     | 1                     | 0     | 1     | 0                     | 0 |               |               |

| 0     | 0     | 1                     | 1     | 0     | 0                     | 0 |               |               |

| 0     | 0     | 1                     | 1     | 1     | 1                     | 1 | (01)          | (01)          |

| 0     | 1     | 0                     | 0     | 0     | 1                     | 0 |               |               |

| 0     | 1     | 0                     | 0     | 1     | 0                     | 1 | (00)          | (11)          |

| 0     | 1     | 0                     | 1     | 0     | 0                     | 1 | (01)          | (10)          |

| 0     | 1     | 0                     | 1     | 1     | 1                     | 0 |               |               |

| 1     | 0     | 0                     | 0     | 0     | 1                     | 0 |               |               |

| 1     | 0     | 0                     | 0     | 1     | 0                     | 1 | (10)          | (01)          |

| 1     | 0     | 0                     | 1     | 0     | 0                     | 1 | (11)          | (00)          |

| 1     | 0     | 0                     | 1     | 1     | 1                     | 0 |               |               |

| 1     | 1     | 1                     | 0     | 0     | 1                     | 1 | (10)          | (10)          |

| 1     | 1     | 1                     | 0     | 1     | 0                     | 0 |               |               |

| 1     | 1     | 1                     | 1     | 0     | 0                     | 0 |               |               |

| 1     | 1     | 1                     | 1     | 1     | 1                     | 1 | (11)          | (11)          |

Q.4 (c) Describe the function that the logic circuit in Part (b) does.

(5 Marks)

**Solution:** From the truth table obtained in Part (b), it is simple to observe that the output F is 1 (truth) if and only if when

$$(A_0 \ A_1) = (B_0 \ B_1)$$

or  $(A_0 \ A_1) = (B_0 \ B_1)$

It is also equivalent to the detection of even numbers of 0s or 1s in the inputs.